Exerciții

Seven-segment display

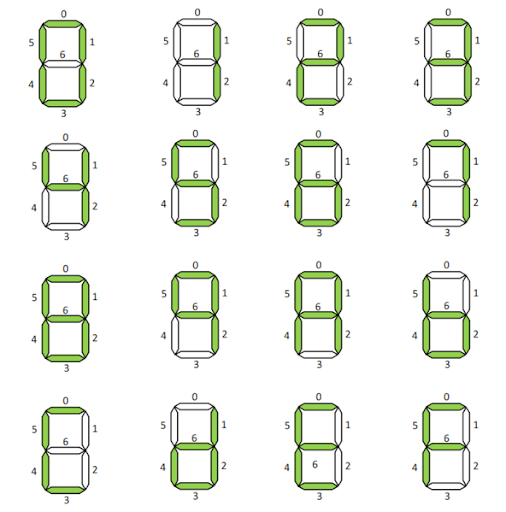

Acest tip de dispozitiv de afișare este alcătuit, așa cum vă puteți da seama și din numele acestuia, din 7 segmente controlabile individual. Așadar, putem aprinde (1 logic) sau stinge (0 logic) fiecare segment din componența acestuia.

Figure: Reprezentarea numerelor în format hexazecimal considerând un afișaj cu 7 segmente

De exemplu, dacă dorim să afișăm cifra 6, ieșirea noastră va avea valoarea ''7’b111_1101''.

Pentru mai multe detalii asupra acestui tip de modul, consultați pagina de Wiki.

Soluția se află în repo-ul materiei GitHub.

- Implementați și simulați un multiplicator pe 4 biți fără a folosi operatorul * (înmulțire).

- Hint: Folosiți convenția Verilog pentru interfața modulului. Câți biți are ieșirea?

- Hint: Înmulțiți pe hârtie, în baza 2, numerele 1001 și 1011. Transpuneți în limbajul Verilog algoritmul folosit.

- Implementați și simulați un modul de afișaj cu 7 segmente pentru numere în baza 10.

- Hint: Există o ieșire validă pentru fiecare intrare? Nu uitați de cazul ''default''.

- Hint: Se vor testa doar cifrele de la 0 la 9.

- Implementați o unitate aritmetico-logică simplă (UAL), pe 4 biți, cu 2 operații: adunare și înmulțire. Folosiți o intrare de selecție de 1 bit pentru a alege între cele două operații astfel: 0 - adunare, 1 - înmulțire.

- Hint: Câți biți au ieșirea sumatorului și a multiplicatorului? Dar a UAL-ului?

- Hint: Pentru selecția dintre ieșirea sumatorului și cea a multiplicatorului se poate folosi atribuirea continuă sau se poate implementa un modul multiplexor 2:1

- Pentru o utilizare mai generală, implementați un UAL cu operatori cu dimensiune variabilă.

- Hint: Pentru a-l implementa, este necesară implementarea unui multiplicator parametrizat - atenție la dimensiunea semnalelor!